Bare Die Embedding von Si, SiC, GaAs

Das Fraunhofer IZM ist Vorreiter in der Erforschung und Entwicklung von Verfahren zur Einbettung (Embedding) elektronischer Bauelemente in Leiterplatten. Das Embedding von Halbleiterchips in die Aufbaulage einer Leiterplatte trägt gegenüber dem konventionellen Drahtbonden zu einer deutlichen Verbesserung der Performance bei. Die elektrischen Verbindungen sind kurz und sehr robust.

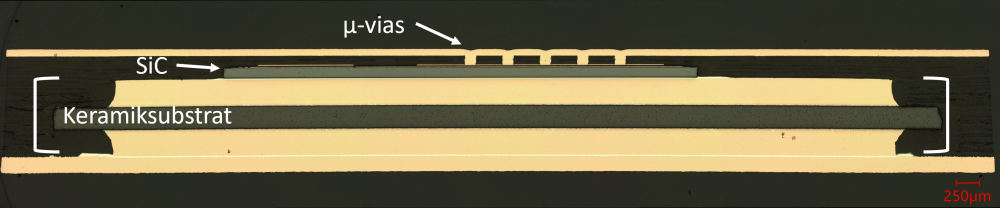

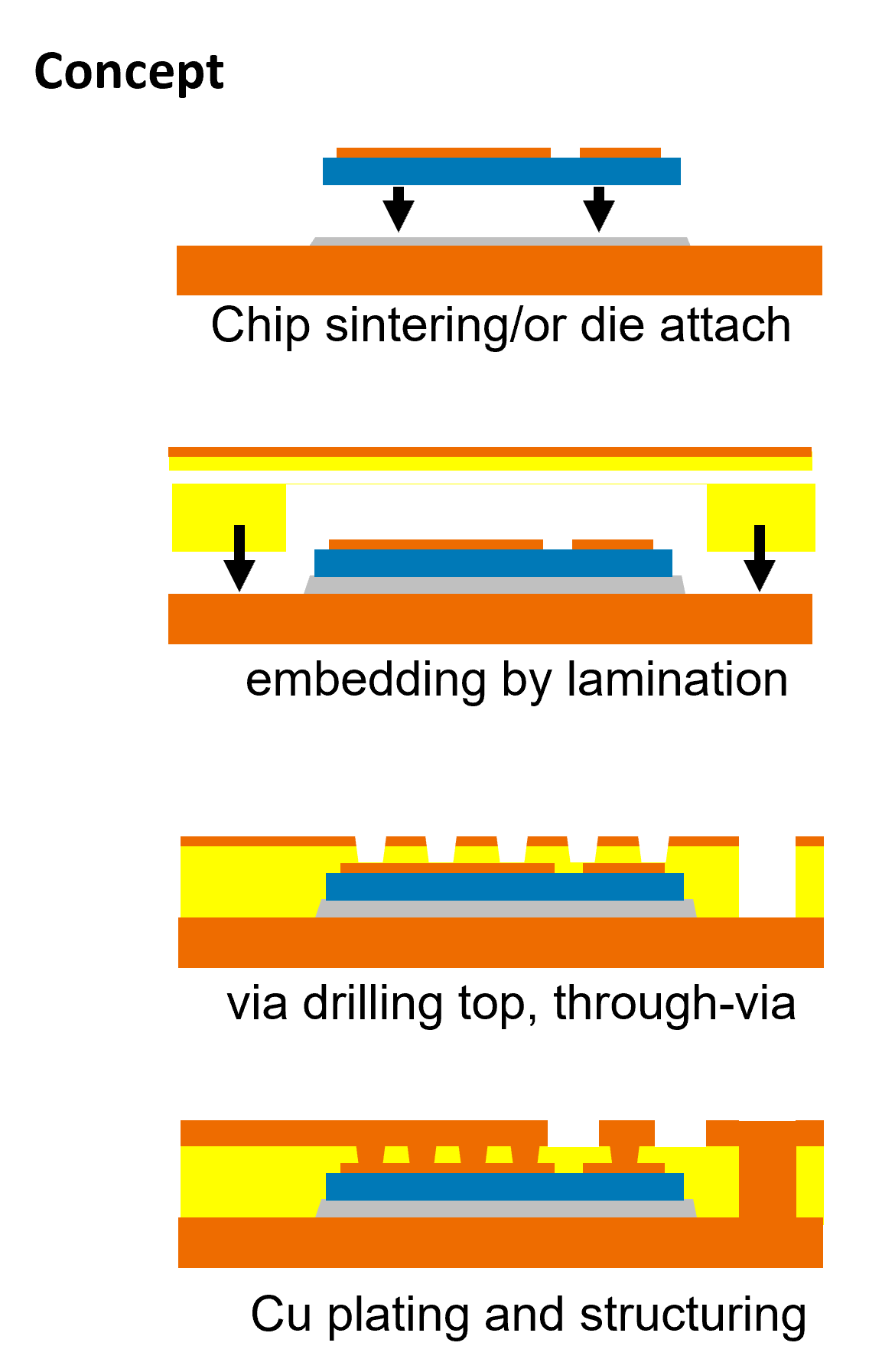

Im Prozess werden die (Si, SiC, SiGe, GaN, oder GaAs) auf ein Substrat mit optimalen thermischen Eigenschaften und der geforderten elektrischen Verdrahtung gesintert oder sinter-geklebt.

Die Chips werden dann in die Aufbaulage der Leiterplatte einlaminiert, so dass sie vollständig von einer Epoxid-Glasfasermatrix umgeben sind. Die elektrischen Kontakte zum embedded Chip werden über galvanisierte µ-vias hergestellt. Als letzter Schritt wird die Kupferlage oberhalb des Chips fotolithografisch strukturiert.

In weiteren Prozessschritten können nun zusätzliche Aufbaulagen über dem embedded Chip realisiert werden.

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM