IZM Panel-HDI / IC Substrate

IC-Substrate: Schlüsselkomponenten für leistungsfähige Halbleiterchips

IC-Substrates (Interposer) dienen der elektronischen Verbindung zwischen den sehr kleinen Kontakten leistungsfähiger Halbleiterchips (ICs; Integrated Circuits) und gröberen Strukturen auf Leiterplatten. Sie nehmen ein Schlüsselrolle bei der Datenübertragung (Signalintegrität, Geschwindigkeit) ein und sind ein grundlegender Bestandteil der fortschreitenden Digitalisierung.

IC-Substrate für das High-Performance Computing: Prototypen und Kleinserien nach Maß

Im Auftrag unserer Kunden entwickeln und fertigen wir Prototypen und Kleinserien von hochdicht mehrlagige verdrahteten IC-Substrates zur Montage von Chips und Chiplets für das Hochleistungsrechnen (High-Performance Computing (HPC)), Quantencomputing und hochintegrierte KI-Anwendungen.

Zum Einsatz kommen fortschrittlichste Packaging-Materialien und Fertigungsverfahren wie z.B. Semi-Additivverfahren.

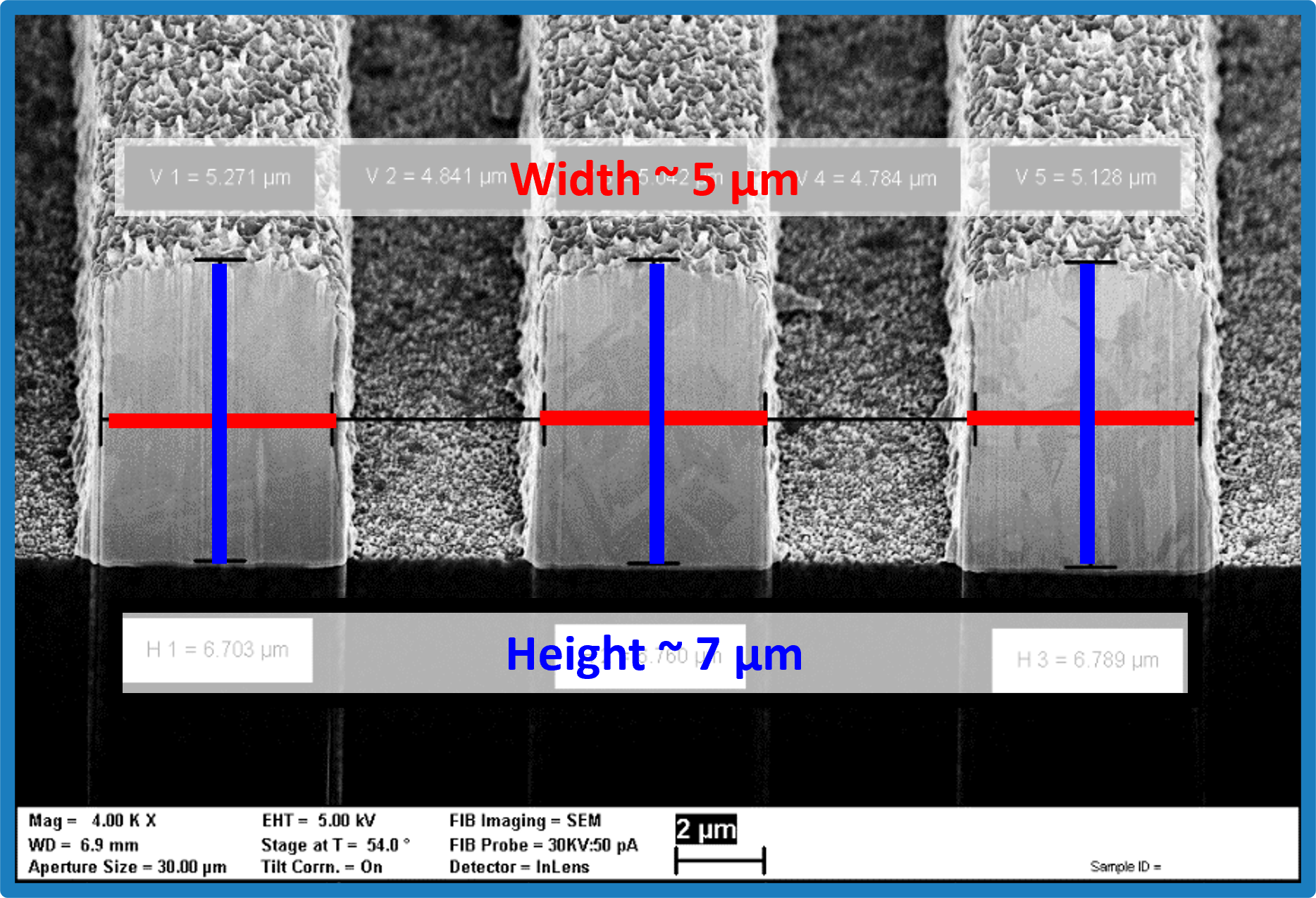

Das Fraunhofer IZM arbeitet auf dem neuesten Stand der Spitzentechnologie in der europäischen Leiterplatten-Industrie. Die aktuellen Line/Space-Werte betragen mindestens 6 µm / 12 µm. Darüber hinaus arbeiten wir auch an der Realisierung von Line/Space-Strukturen mit 2 µm / 2 µm für zukünftige Chip-Generationen.

Transparenz und Dokumentation für erfolgreichen Wissens- und Technologietransfer

Um Ideen und Innovationen erfolgreich in die Wirtschaft zu transferieren, ist Transparenz erforderlich. Daher gewähren wir unseren Kunden einen vollständigen Einblick in unsere Prozesse und Materialien, um eine umfassende Transparenz im Rahmen unserer Zusammenarbeit sicherzustellen. Eine ausführliche Dokumentation ist dabei stets integraler Bestandteil jedes Projekts.

Technische Daten

IC-Substrate:

- 20 – 5 µm Standard

- 5 – 2 µm F&E

PCB-Dicke:

- 50 – 20 µm

Semi-Additive-Processing (SAP)

- Format: 610 x 457 | 510 x 515 mm²

- Gesputteret Basisschicht für die galv. Abscheidung

- Maskenlose Strukturierung (LDI)

- Kupfergalvanik zu Füllen der µ-vias und Aufbau der Leiterstrukturen

- Entfernung der Maskenschicht und selektives Ätzen der Basisschicht

Advanced SAP @ IZM

- Ultra-dünne Basisschicht

- Verarbeitung neuester Maskenmaterialien

- Neu Dielektrika PID, BU, PPG, RCC

- photo- and plasma-process für µ-vias

- Neu: trockene Prozessierung auf panel leven: Veraschung der Maskenschicht im Plasma und reaktives Ionenätzen für die Basisschicht

- Galvanik auf Vollformate zur Herstellung von CuNiSnAg Pillars

Anwendungsbereiche von HPC:

- Glasskern-Substrate (GCS),

- Packaging auf Vollformat (PLP)

- IC-Substrate

- Quantencomputing

- High performance computing

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM