RealIZM Blog

Pionierarbeit für die Mikroelektronik von morgen: Von der Chiplet-Integration bis zum Cooling – Herausforderungen beim High-End Performance Packaging

Die Zukunft der Mikroelektronik steht vor spannenden Entwicklungen und wichtigen Trends. Doch wie wird sich diese technologische Branche in den kommenden Jahren weiterentwickeln? Welche Anwendungsbereiche treiben die 2,5D-/3D-Hetero-Integration und das High-End Performance Packaging maßgeblich voran und wo liegen die Grenzen des physikalisch Möglichen?

Anlässlich des 30-jährigen Jubiläums des Fraunhofer IZM traf sich RealIZM, der Wissenschaftsblog für Mikroelektronik des Instituts, mit Prof. Dr.-Ing. Martin Schneider-Ramelow. Der Institutsleiter gibt einen umfassenden Einblick in die Zukunft der Mikroelektronik sowie in aktuelle und geplante Forschungsaktivitäten.

RealIZM: Wie stellen Sie sich die Zukunft der Mikroelektronik vor? Welche wichtigen Trends werden Ihrer Meinung nach die kommenden Jahre prägen?

Tatsache ist, dass wir in Europa nicht die Logik- und die Memory-Bausteine mit den feinsten Strukturbreiten innerhalb der Halbleiter (Nodes) produzieren werden, selbst wenn große Hersteller wie Intel oder TSMC sich hier ansiedeln wollen. Auf diesem Gebiet sind bekanntlich nur einige wenige große internationale Hersteller tätig, die den Maschinenpark und Aufwand betreiben können, um Nodes kleiner als 5 nm herzustellen. Aber es wird immer wichtiger, diese Bauelemente mit anderen Bausteinen, die andere innere Strukturen aufweisen, mit Sensorik, Leistungselektronik, Spannungsversorgung usw. zusammenzubringen.

Am Fraunhofer IZM forschen und arbeiten wir bereits seit vielen Jahren an der 2,5D-/3D-Hetero-Integration. Die Ausstattung und die Möglichkeiten, die unser Institut zur Forschung und Entwicklung auf diesem Gebiet hat, sind einzigartig in Europa. Das hat mich bestärkt, dem Haus solange verbunden zu bleiben und den Ruf als Institutsleiter anzunehmen.

Einige Firmen sprechen bereits von der 5,5D-Hetero-Integration. Gemeint ist die Kombination aus 2,5D und 3D. Das heißt, Chips werden übereinandergestapelt und elektrisch miteinander verbunden und zusätzlich auf einem Interposer oder organischen Substrat miteinander verbunden, auf dem sich weitere Bauelemente sowie Halbleiter oder Chiplets befinden. Beim Packaging zeichnet sich der Trend ab, immer weiter in die Breite und Höhe zu gehen. Unser Institut für Mikrointegration ist in diesem Bereich sehr gut aufgestellt. Unser Ziel ist, hierbei auch weiterhin eine Vorreiterrolle einzunehmen.

RealIZM: Welche Anwendungsbereiche treiben die 2,5D-/ 3D-Hetero-Integration maßgeblich voran?

Es sind genau die Schlagwörter, die seit 3 bis 5 Jahren in der Fachwelt zu hören sind. Die Nachfrage nach Hochleistungsanwendungen im Zusammenhang mit Rechenzentren, High Performance Computing (HPC), Quantencomputing und neuromorphem Rechnen, Smart Sensing, Optoelektronik, 5G- und 6G-Kommunikation, Künstlicher Intelligenz (KI) und auch dem Autonomen Fahren steigt stetig an.

Zum einen treibt das Training und die Inferenz der KI die Nachfrage nach Servern für Rechenzentren an. Zum anderen werden zunehmend mehr Supercomputer eingesetzt, um komplexe Aufgaben wie z.B. die Darstellung digitaler Zwillinge und Berechnungen für die Klimaforschungen und Quantenmechanik auszuführen. Nicht zuletzt erfreuen sich Cloud-Computing und Video-Streaming zunehmender Beliebtheit. Bei all diesen Anwendungen entstehen extrem viele Daten. Deren Verarbeitung und Übertragung erfordert ein viel besseres Computing. Mit der 3D-Hetero-Integration leistet das Fraunhofer IZM einen wichtigen Beitrag dazu.

RealIZM: Wenn die Leiterbahnen zukünftig noch enger, die Via-Durchmesser noch kleiner und die Wafer-Dicken noch dünner werden – wann erreichen wir die Grenze des physikalisch Möglichen?

Im Zusammenhang mit dem Mooreschen Gesetz hieß es vor einigen Jahren, dass mit den feinen inneren Strukturen langsam Schluss sein wird. Einige führende Hersteller haben angekündigt, in Zukunft auf Nodes von kleiner 5 nm zu setzen. Vor einigen Jahren konnte sich das noch niemand vorstellen. Auch bei den feineren Strukturen auf der Leiterplatte also den organischen Substraten zeichnet sich ein neuer Trend bei den feineren Strukturen ab, der den unteren einstelligen Mikrometer-Bereich anstrebt. Noch ist das nicht State-of-the-Art. Ich bin überzeugt, dass die Kolleg*innen an unserem Institut diese Thematik maßgeblich weiter vorantreiben werden. Der Grundstein, in noch kleinere Bereiche vorzudringen, ist bereits gelegt. Zum einen wenden wir neue Technologien wie das Hybrid-Bonding an. Zum anderen stehen uns dank großer Forschungs- und Fördermaßnahmen zahlreiche neue Geräte zur Verfügung, mit denen sich noch kleinere Strukturen umsetzen lassen.

Seit 2022 ist das Fraunhofer IZM mit dem QuantumPackagingLab eine der führenden Anlaufstellen für die Entwicklung zuverlässiger Packaging-Ansätze rund um die Quantenphotonik. Unsere Expert*innen für optische Verbindungstechnik verfügen beispielsweise über einen speziellen 3D-Drucker zur Laserbearbeitung von Glas mit einer Genauigkeit von etwa 1 μm bei 200 x 200 mm. Nach unserer Kenntnis sind bisher nur 10 Maschinen weltweit in diesem Forschungskontext im Einsatz. Das Gerät ist für vier Verfahren ausgelegt: selektives laserinduziertes Ätzen von Glas, Schweißen von Glas, Schreiben von 3D-Wellenleitern und 2-Photonen-Polymerisation. Normalerweise ist für jeden dieser Prozesse eine einzelne Maschine notwendig.

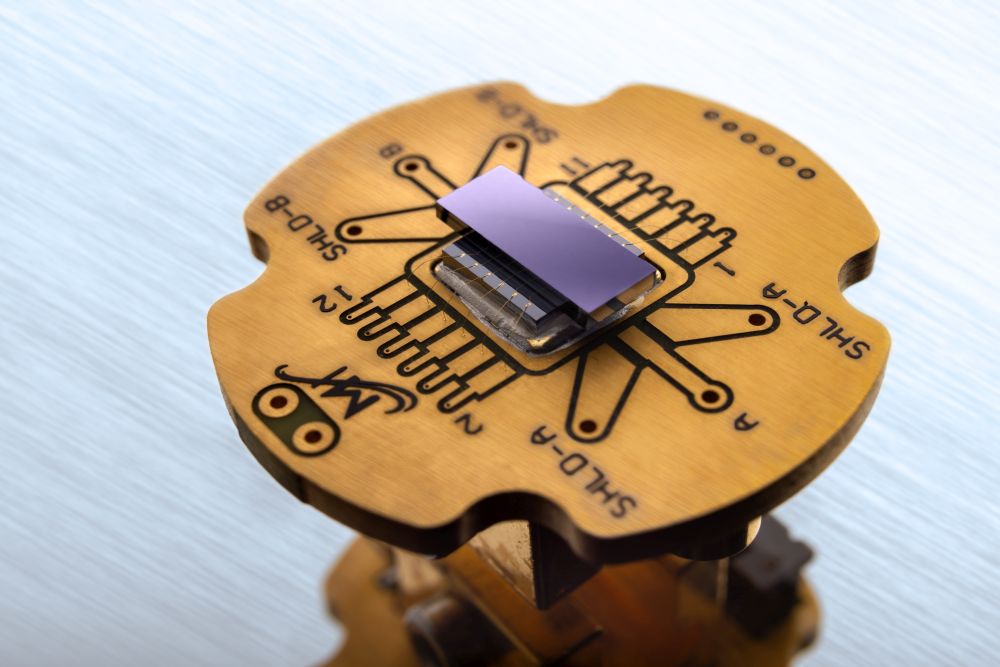

Quantentechnologien und Highspeed-Rechner mit Supraleitern gehören zu den aktuellen Elektronik-Trends. Doch sind die Strukturen, mit denen etwa Qubits auf Chips angesteuert und in Echtzeit ausgelesen werden können, bislang noch größer als die Qubits selbst. Eine Forschungsgruppe unseres Instituts hat jüngst einen Prozess entwickelt, mit dem sie die Anschlussdichte mit Indiumbumps im Vergleich zu bisherigen Lösungen verdoppeln. Mit dieser Technologie wollen sie nun die Ansteuerelektronik optimieren. Zusätzlich haben wir an unserem Berliner Standort ein Kryomesslabor eingerichtet, mit dem die Leistungsfähigkeit der Elektronikaufbauten bei Temperaturen von wenigen Kelvin getestet werden kann.

Um auf die Ausgangsfrage zurückzukommen, wir werden irgendwann tatsächlich nicht mehr kleiner werden können. Letztendlich wird die bereits von Rack zu Rack genutzte photonische Datenübertragung auch direkt in die Leiterplatten gehen sowie von Chip-to-Chip erfolgen. Daran arbeiten wir bereits seit einigen Jahren.

RealIZM: Vor einigen Wochen haben die Forschungsfabrik Mikroelektronik Deutschland (FMD) und Intel gemeinsam mit Schlüsselakteuren der deutschen Industrie eine Roadmap 2030+ für die Forschung im Bereich der 3D-Integration vorgestellt. Welchen Beitrag wird das Fraunhofer IZM dafür leisten?

Einerseits hat unser Institut eine wichtige Rolle bei der Gesprächsanbahnung mit Intel gespielt. Wir arbeiten seit vielen Jahren eng zusammen. Der jetzt vorgestellte Forschungsfahrplan wurde in einer Reihe von Workshops erarbeitet, die von der FMD und Intel Europe Research organisiert wurden. Der erste Workshop fand bei uns in Berlin am Fraunhofer IZM statt.

Andererseits haben wir aktiv an der Entwicklung der Roadmap mitgewirkt und bereiten gemeinsam mit den beteiligten Akteuren die Grundlagen der zukünftigen Mikroelektronik vor. Es ist von großer strategischer Bedeutung, dass der Standort Europa nicht den Anschluss verliert und zukünftige Entwicklungen im Schulterschluss mit Industriepartnern gefördert und vorangetrieben werden. Über Chiplets wird seit vielen Jahren geredet. In der Produktion sind aber weltweit erst kleine Mengen. Wir sind noch weit davon entfernt fertige Chipletlösungen zu liefern, aber der Fahrplan für die Umsetzung in den kommenden Jahren steht.

Für den Einsatz im Automotive-Bereich müssen zukünftig Nodes mit feinsten Strukturen mit Sensorik, MEMs, photonischen Elementen, LiDAR sowie Radar und vielem mehr kombiniert werden. Die dabei entstehenden Datenmengen müssen verarbeitet werden. Wir am Fraunhofer IZM sind davon überzeugt, dass dies zukünftig nur mit Chiplets möglich sein wird. Die Halbleiter und Komponenten aus den verschiedenen Fabs, von den Fraunhofer-Instituten oder anderen europäischen Forschungs- und Technologieorganisationen (RTOs) müssen ganz eng auf kleinstem

Raum miteinander verbunden werden. Technologien wie unser Panel Level Packaging spielen dabei eine wichtige Rolle. Fakt ist, am Ende muss alles auf ein Substrat integriert werden, um die Chiplets mit den anderen Komponenten zu verbinden. Bevor eine Massenfertigung starten kann, sind zentrale Fragen zu klären: Wer sind die möglichen Abnehmer für diese Bausteine? Welche Kooperationsmöglichkeiten mit der Industrie gibt es in Deutschland und in Europa?

RealIZM: Auf der aktuellen Institutsbroschüre ist eine Visualisierung eines High-End Performance Packages (HEPP) abgebildet. Was hat es mit dieser Abbildung auf sich und was genau macht ein HEPP aus?

Die Grafik visualisiert, wie verrückt die Systeme werden, wenn sie hochfunktional sein sollen und welche Technologien dafür notwendig sind. Wir zeigen fiktiv auf, was heute bereits alles beim High-End Performance Packaging gemacht wird und wo unser Institut auf dem Gebiet der Hetero-Integration aktiv ist. Wir bringen Chips auf und in die Leiterplatte. Wir bauen Interposer, stapeln Chips und verarbeiten MEMS in Systemen. Wir kümmern uns um das Cooling, Antennen und die Datenübertragung. Das Fraunhofer IZM ist das Packaging-Institut in Deutschland, Europa und weltweit.

Die derzeitige Herausforderung besteht darin, dass die Industrie neue Maßstäbe setzt, was die feineren Strukturen, Mikro-Bumps, Fine Lines und Spaces angeht. Um hierbei mitzuhalten und selbst Innovationen zu liefern, benötigen wir die neuesten Maschinen und Messtechniken. Unser Beitrag ist es, Systeme zu entwickeln und aufzubauen, die die Industrie dann produzieren kann. Während wir das Gesamtkonzept betrachten, konzentrieren sich die Firmen auf bestimmte Entwicklungsbereiche z.B. auf das Packaging, die Entwicklung des Chip-Designs oder die Herstellung von Chips, MEMS oder Sensoriken. Aus diesen einzelnen Bausteinen muss am Ende jedoch ein funktionsfähiges System entstehen.

Wir verstehen uns als Bindeglied zwischen den Herstellern der Materialen, Maschinen, Komponenten und den Spezialisten der Aufbau- und Verbindungs-Technik. Als anwendungsorientiertes Forschungsinstitut ist unser Ansatz, zu verstehen, was die jeweilige Anwendung für Bedarfe und Anforderungen an Technologien, Komponenten und Materialien sowie Zuverlässigkeit hat. Bei den Vorbereitungen für den Europäischen Chips Act (ECA) stehen wir im Zentrum aller Aktivitäten.

Datenschutz und Datenverarbeitung

Wir setzen zum Einbinden von Videos den Anbieter YouTube ein. Wie die meisten Websites verwendet YouTube Cookies, um Informationen über die Besucher ihrer Internetseite zu sammeln. Wenn Sie das Video starten, könnte dies Datenverarbeitungsvorgänge auslösen. Darauf haben wir keinen Einfluss. Weitere Informationen über Datenschutz bei YouTube finden Sie in deren Datenschutzerklärung unter: https://policies.google.com/privacy

RealIZM: Im Zusammenhang mit Advanced Packaging ist immer häufiger vom Hybrid-Bonding und der Chiplet-Integration zu lesen. Auf der anderen Seite müssen beim Packaging von modernen Leistungshalbleitern wie Siliziumkarbid (SiC) oder Galliumnitrid (GaN) neue Wege beschritten werden. Wie ist das Fraunhofer IZM hierzu aufgestellt?

Wie bereits erläutert, fokussiert sich die Mikroelektronikindustrie seit einigen Jahren verstärkt auf die heterogene Integration, um mehr Rechen-, Speicher- und andere Funktionen auf einer bestimmten Fläche zu integrieren. Um die 3D-Verbindungsdichte zu erhöhen, werden mehrere fortschrittliche und/oder ausgereifte Chips in einem einzigen Gehäuse untergebracht. Bei Hochleistungsanwendungen schrumpft die Anforderung an den IO-Abstand jedoch unter das Maß, das mit Flip-Chip-Verbindungen erreicht werden kann. Um Chiplets mit einem Abstand von 10 μm miteinander zuverlässig zu verbinden, ist die Hybrid-Bonding-Technologie derzeit die einzige Option.

Seit mehreren Jahren arbeiten wir an unserem Standort in Sachsen in Industrie-Projekten an dem Thema Hybrid-Bonding. Bisher arbeiten wir mit Verbindungsbreiten von 4, 5 - 6 Mikrometern. Um in einen Bereich auf die Hälfte herunterzukommen sind derzeit Kooperationen notwendig, da wir noch nicht über den dafür notwendigen Maschinenpark verfügen. Aber wir planen über Förderprogramme (u.a. den ECA) die dafür notwendigen Geräte anzuschaffen. Wir wissen, wie und unter welchen Bedingungen das im Reinraum funktioniert. Für die erwarteten Strukturen im Sub-Mikrometerbereich zum Ende dieses Jahrzehnts sind noch umfangreiche Entwicklungen zu leisten.

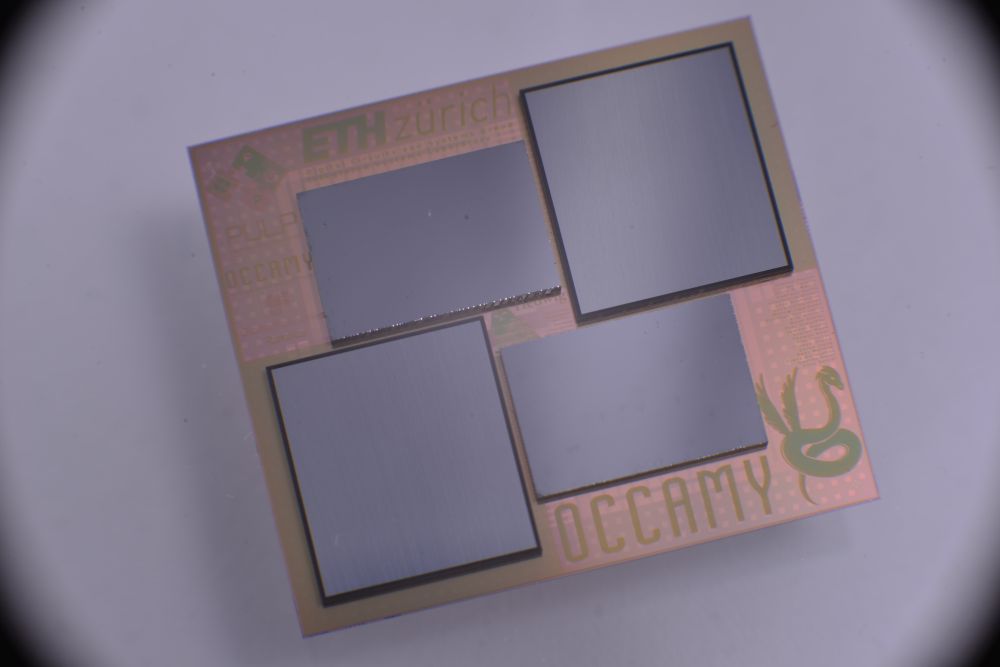

Auch bei dem Thema Chiplets haben wir eine Vorreiterrolle inne. Wir arbeiten sowohl auf Silizium- und Glas-Interposern und eruieren zudem, die Möglichkeit auf organischen Substraten zu arbeiten. Es ist zu erwarten, dass in den nächsten Jahren die inneren Chip-Strukturen bei einigen Halbleitertypen auf einen Bereich von unter 2 nm runtergehen. Was die Ankontaktierung dieser Chips auf Substraten betrifft, sind bei den Substraten in Asien bereits erste IC-Substrate mit zwei Mikrometern Lines und Spaces (L/S) in der Anwendung. Jedoch sind hier noch eine Reihe technischer Fragestellungen zu beantworten, z.B. ob die Hochfrequenz-Tauglichkeit und die Signal-Integrität gegeben sind und wie findet die Entwärmung des Systems statt? Das sind genau die Herausforderungen, die mich auch persönlich motivieren.

Wichtig zu verstehen ist, dass das Fraunhofer IZM keine Halbleiter fertigt, d.h. wir sind kein CMOS-Institut, welches Chips designt und fertigt. Wir fangen beim Wafer an. Wenn aber zukünftig auch die Außenanschlüsse der Chips und andere Bauelemente immer kleiner werden und als System auf ein organisches, glasbasiertes oder keramisches Substrat gebracht oder gar in die Leiterplatte eingebettet werden sollen, ist noch einige Entwicklungsarbeit notwendig. An dieser Stelle kommt das Fraunhofer IZM wieder ins Spiel. Unsere zwei Haupttechnologien sind zum einen das Wafer Level Packaging und zum anderen die (Large Area)-Substrat-Systemintegration, die beide stringent weiterentwickelt werden. Mit Hilfe der Leiterplatten-Technologie haben wir Leistungs-Halbleiter teilweise mit keramischen Interposern eingebettet, um hoch performante Leistungselektronik zu realisieren. Dafür bauen wir Subsysteme, Module und Systeme und kümmern uns auch um das Gehäuse und die Kühlung. Unser Institut ist seit vielen Jahren bei der ECPE, dem europäischen Kompetenzzentrum für Leistungselektronik, in der Vorentwicklung mit unseren Zukunftsthemen engagiert. Ich bin mir sehr sicher, dass wir zukünftig wesentliche Beiträge für die Mikroelektronik leisten werden. Fest steht, in den kommenden 30 Jahren gehen uns die Forschungsthemen nicht aus.

RealIZM: Welche Ideen und Pläne gibt es für die zukünftige Gestaltung der drei Standorte des Fraunhofer IZM in Berlin, Dresden und Cottbus?

Seit 2019 wird der Innovationscampus für Elektronik und Mikrosensorik Cottbus – iCampμs Cottbus - unter Beteiligung von sechs außeruniversitären Forschungseinrichtungen sowie Professoren der BTU Cottbus-Senftenberg etabliert. Unser Institut ist an verschiedenen Projekten im Bereich Hochfrequenz- und Highspeed-Systeme und Antennenkonfigurationen beteiligt. Ein Beispielprojekt ist die Entwicklung eines mobilen Ultra-Low Power Radarsystems für Medizinanwendungen. Ich freue mich sehr, dass wir seit Anfang 2023 auch mit einer Professur im Bereich der Hochfrequenztechnik am iCampμs Cottbus vertreten sind.

Im kommenden Jahr findet die iCampμs Cottbus Conference (iCCC2024) statt, zu der ich alle aus Forschung und Wirtschaft herzlich einlade. Die Transferkonferenz für Innovationen in Wissenschaft und Industrie zeigt Potenziale und neue Anwendungen auf, die sich durch leistungsstarke Sensorik, den Einsatz innovativer Mikroelektronik und KI für die Industrie 4.0, Energiewirtschaft und (Tele-)Medizin ergeben. Ich habe große Hoffnung das Fraunhofer IZM-ASSID an unserem Standort in Dresden langfristig auszubauen. Anders als in Berlin, ist das Gelände in Moritzburg im Besitz der Fraunhofer Gesellschaft. D.h. wir haben dort die Möglichkeit – vorausgesetzt das Geld in einem unteren dreistelligen Millionen-Euro-Bereich ist verfügbar – die vorhandene Reinraumfläche zu verdoppeln und mit einem entsprechenden Maschinenpark auszustatten.

Es wäre toll, wenn das Fraunhofer IZM-ASSID im Sinne der Souveränität für Deutschland über eigene Fertigungskapazitäten verfügen würde. Ich glaube, wir könnten zukünftig anspruchsvolle Module, Submodule, kleine Systeme und Vorprodukte liefern. Diesen Weg einzuschlagen, unterstütze ich gern. Voraussetzung dafür sind die finanziellen Mittel und auch der Nachfragebedarf vonseiten der Industrie. Das ist jedoch noch alles Zukunftsmusik.

Eine andere Option ist, sich in bestehende bzw. geplante Reinräume einzumieten. Gemeinsam mit dem Fraunhofer IPMS haben wir am Centers Nanoelectronic Technologies (CNT) in Dresden dazu eine Lösung gefunden. Im Sommer 2022 wurden gemeinsam mit dem IPMS die neuen Reinräume des CNT und das 300mm Center for Advanced CMOS & Heterointegration in Dresden-Moritzburg eröffnet. Wir planen in den kommenden fünf Jahren zusätzliche Reinraumkapazitäten mit bis zu 900 m2 zu schaffen und mit einem Gerätepark auszustatten, um gemeinsam mit dem Fraunhofer IPMS und CNT zusammenzuarbeiten.

Wir müssen hierbei auf die neuesten Maschinen zurückgreifen und Reinraumkapazitäten planen, um mit den Entwicklungen beim High-End Performance Packaging mithalten zu können. Wir kooperieren daher mit zahlreichen Partnern – Maschinen-, Material-, Anwender- und Packaging-Spezialisten. Dank diverser Fördermaßnahmen und unserer Reinräume ist uns dies bisher sehr gut gelungen. Unser Standort in Berlin profitiert aktuell vor allem von der Förderung durch das Bundesministerium für Bildung und Forschung (BMBF) für das Projekt „Forschungsfabrik für Quanten- und neuromorphes Computing“ (FMD-QNC). Die bestehenden Räumlichkeiten werden laufend optimiert und modernisiert sowieTechnologien weiterentwickelt.

RealIZM: Das Fraunhofer IZM trägt neben dem Begriff der Mikrointegration den Begriff Zuverlässigkeit im Namen. An welcher Stelle sollten Zuverlässigkeitsbewertungen idealerweise ansetzen?

Die Zuverlässigkeit von Elektronik ist die Basis für funktionierende Systeme. Am Fraunhofer IZM betrachten wir das High-End Performance Packaging also die Heterosystemintegration von den Materialien, Komponenten und Maschinen über die Aufbau- und Verbindungstechnologien sowie Test, Charakterisierung und Zuverlässigkeit bis zur Anwendung als Ganzes. Wir sind daher besonders stark in der Physics-of-Failure-Analysis. D.h. wenn wir neue Systeme mit neuen Materialien und feineren Strukturen bauen, dann wissen wir je nachdem in welches Anwendungsgebiet diese fließt, welche Beanspruchungen zu erwarten sind. So können wir gezielt elektronische Systeme zuverlässig ausrichten und simulieren. Für uns interessant ist, wenn wir die Simulation auf die von uns neu entwickelten Technologien und neu eingesetzt Materialien anwenden. Wir machen nicht nur die Zuverlässigkeitstests und -analysen, sondern beschreiben darauf basierend den Fehler- und Versagensmechanismus. Was nutzt es, ein System aufzubauen, dass in der Anwendung nach zwei Tagen defekt ist.

Die Bewertung der Zuverlässigkeit muss auf abgestimmten Technologieebenen erfolgen und setzt zwingend das Verständnis für das jeweilige System voraus. Wo, wie und wann wird das Bauteil verbaut und welchen Stressfaktoren (Temperaturhöhe und -wechsel, Feuchtebeanspruchung, Belastungsdauer, etc.) ist es dabei ausgesetzt? Messungen zur Zuverlässigkeit sollten so frühzeitig wie möglich im Prozess erfolgen.Die Notwendigkeit einer technologiebegleitenden Zuverlässigkeitsanalyse wird bei dem Thema Chiplets eine immer größere Rolle spielen. Werden Chips von unterschiedlichen Herstellern und Technologie in einem Multi-Package verbaut, reicht im schlimmsten Fall ein „schlechter“ Chip oder ein unzureichender Interconnect aus, um zum Ausfall des Gesamtsystems zu führen.

RealIZM: Nach all den Einblicken hat man das Gefühl, es herrschen goldene Zeit für die Mikroelektronik. Ist dem tatsächlich so oder gibt es auch Herausforderungen?

Die Notwendigkeit, die Maschinenparks stetig zu erneuern, und die Reinrauminfrastruktur vorzuhalten und zu betreiben, sind kostenintensiv. Hinzu kommt der Fachkräftemangel. Am Berliner Standort haben wir aktuell über 100 Labore auf einer Gesamtfläche von 8.000 m2. Um dies alles zu bespielen, brauchen wir aufstrebende Wissenschaftler*innen und Techniker*innen. Wir bilden seit über 20 Jahren angehende Mikrotechnolog*innen aus. Unser Forschungsinstitut bietet spannende Aufgaben und Perspektiven, sich weiterzuentwickeln, bereits für Studierende und nach dem Studienabschluss erst recht.

Ein aktuelles Schlagwort in der Branche lautet Souveränität. Um wesentliche Vorentwicklungen für die Industrie leisten zu können, benötigen Forschungsinstitute die finanziellen Mittel für den Aufbau und den Betrieb einer entsprechenden technischen Infrastruktur. Mein Appell an unsere Zentrale in München und auch an die Entscheidungsträger*innen in der Politik lautet: Die kontinuierliche Investition in die Aus- und Fortbildung von Fachkräften für die Mikroelektronik und die Ausstattung der Forschungsinstitute lohnt sich und wird auch weiterhin notwendig sein. Wir haben bereits sehr viel erreicht. Dank dem Europäischen Chips Act (ECA) und zahlreichen Initiativen wie der FMD-Förderung durch das BMBF und dem o.g. „FMD-QNC“ beobachte ich eine zunehmende Vernetzung auch mit europäischen Forschungsorganisationen wie imec und CEA-Leti. Nur gemeinsam können wir Lösungen für die aktuellen und zukünftigen Herausforderungen in der Elektronikforschung erarbeiten.

Bei aller Technikeuphorie gilt es auch, die Auswirkungen der neu entwickelten Technologien auf die Umwelt und deren Energieeffizienz zu berücksichtigen. Fakt ist, es wird immer mehr Elektronik verbaut. Wenn zukünftig medizinische Operationen mit Unterstützung eines digitalen Zwillings ausgeführt werden oder Fahrzeuge autonom fahren, bedeutet das auch einen höheren Energiebedarf. Die Themenfelder, neue elektronische Produkte auf einem möglichst niedrigen Energieniveau zu betreiben, über deren Wiederverwertung bis hin zur Reparierbarkeit nachzudenken, gewinnt immer mehr an Bedeutung in der Elektronik und der Aufbau- und Verbindungstechnik.

Mit den Auswirkungen des technischen Fortschritts auf den ökologischen Fußabdruck befasst sich das Fraunhofer IZM seit seiner Gründung. Wir sind seit 30 Jahren auch international Vorreiter auf diesem Gebiet. In der Anfangszeit unseres Instituts haben wir das Thema „bleifreie Elektronik“ intensiv bearbeitet und seitdem die elektronikspezifischen Nachhaltigkeitsthemen immer weiterentwickelt. Unsere Arbeit auf diesem Gebiet mündet gerade in dem Projekt „Green ICT @ FMD“. Hier wird geschaut, wie nachhaltig Elektronik sein kann. Wir schauen uns z.B. die Stoffkreisläufe und den CO2-Fußabdruck von Elektronik in all den Bereichen an, in denen High-End Performance Packaging zum Einsatz kommt. Unsere Aufgabe ist das, was wir im High-End Performance Packaging entwickeln und aufbauen, holistisch zu betrachten. Es reicht nicht aus, die innovativsten Packaging-Verfahren zu haben. Wir müssen zugleich sicherstellen, dass die von uns eingesetzten Technologien zuverlässig funktionieren und zugleich auch nachhaltig sind.

Hintergrundinformation zu Prof. Dr.-Ing. Martin Schneider-Ramelow

Hintergrundinformation zu Prof. Dr.-Ing. Martin Schneider-Ramelow Professor Martin Schneider-Ramelow hat sich als einer der führenden Mikroelektronik-Forscher und -Lehrer in Deutschland etabliert. Seit 2014 hat er eine Honorarprofessur an der TU Berlin und seit Januar 2017 die Professur für “Werkstoffe der Hetero-Systemintegration“ am Institut für Hochfrequenz- und Halbleiter-Systemtechnologien der Fakultät IV Elektrotechnik und Informatik der TU Berlin inne und leitet den Forschungsschwerpunkt Technologien der Mikroperipherik.

Seit 2023 ist Martin Schneider-Ramelow Institutsleiter am Fraunhofer IZM und befasst sich mit der thematisch-strategischen Ausrichtung der Institutsaktivitäten, der Weiterentwicklung des Instituts im Rahmen der European Chips Act Initiative und der Vertiefung der Kooperation mit Universitäten und Instituten. Darüber hinaus sind ihm die über 400 Mitarbeitenden und deren Weiterentwicklung sehr wichtig. Als Professor betreut er zudem zahlreiche Promovenden und Graduierte und entwickelt Mentoring-Programme und Personalcoachings.

Martin Schneider-Ramelow ist Autor und Co-Autor von über 250 Fachartikeln. Er gilt als Spezialist auf dem Gebiet der Qualität und Zuverlässigkeit metallischer Interconnects und ist weltweit anerkannt als Experte für Drahtbondverbindungen. So war er als Obmann der Arbeitsgemeinschaft 2.4 „Bonden“ im Deutschen Verband für Schweißen und verwandte Verfahren (DVS) maßgeblich an der Neuverfassung des über 20 Jahre alten DVS-Standards 2811 beteiligt, der nun seit 2017 als Grundlage für die Bewertung von hochqualitativen Drahtbondverbindungen gilt. Ferner ist er Mitglied von 6 nationalen und internationalen Konferenzprogrammkommissionen auf dem Gebiet des Electronic Packagings, Senior Member IEEE, Fellow IMAPS USA und seit 14 Jahren 1. Vorsitzender der International Microelectronics and Packaging Society (IMAPS) Deutschland.

Letzte Änderung:

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM