High-End Performance Packaging - das neue Paradigma der Elektronikintegration

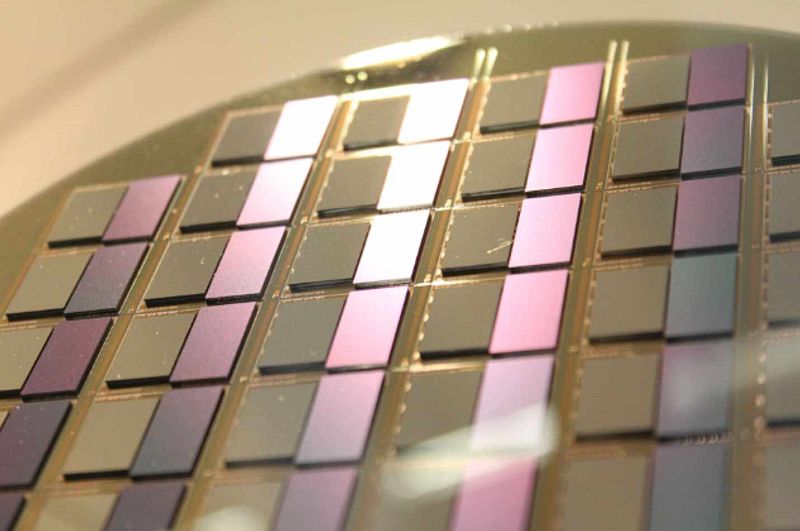

Chiplets

In der heutigen Welt hat das „Advanced Packaging“ mit Ansätzen wie Flip-Chip-Technologien, Wafer Level CSPs oder in das Substrat eingebetteten ICs eine Schlüsselfunktion innerhalb der modernen Elektronik-Integrationstechnologien.

Angesichts der ständig steigenden Nachfrage nach schnelleren und effizienteren Computer-und Elektroniksystemen ist der Bedarf an innovativen und fortschrittlichen Packaging-Lösungen zudem größer denn je.

Industrie und Forschung haben auf diesen Trend mit der Einführung neuer Techniken und Architekturen wie Chiplets und heterogener Integration reagiert, die Hochleistungssysteme zu geringeren Kosten versprechen.

Dieser Trend geht einher mit einer Verlagerung des Systemaufbaus weg von passiven Systemträgern (d.h. Interposer, High-End-Substrate), hin zu Trägern, die eine aktive Rolle für die Funktionen des (Teil)-Systems spielen.

Hierbei ebnete das Aufkommen der Chiplet-Architektur den Weg und beeinflusste diesen Trend stark. Unter Chiplets versteht man kleinste Chip-Untereinheiten, die sowohl monolithisch als auch, was noch wichtiger ist, nicht-monolithisch zu einer vollständigen Systemfunktionalität kombiniert werden können und somit den „System-on-Chip“-Ansatz flexibel unterstützen.

Jedes Chiplet ist so konzipiert, dass es zunächst unabhängig eine eigenständige Funktion bietet und mit weiteren Chiplets modular kombiniert wird, um eine maßgeschneiderte Lösung für kundenspezifische Anwendungen zu schaffen.

Dies stellt – sowohl für Systemdesign wie auch -herstellung – einen äußerst flexiblen und skalierbaren Ansatz dar und ermöglicht eine schnellere Markteinführung sowie geringere Entwicklungskosten innovativer Produkte.

Die Vorteile des Chiplet-Ansatzes liegen auf der Hand: Durch die Zerlegung des zuvor monolithischen Single-Chip-Designs in kleinere, besser handhabbare Komponenten können die Entwickler die Vorteile bestehender, bewährter Technologien nutzen und sich gezielt auf die Entwicklung neuer und innovativer Komponenten konzentrieren. Dies resultiert in einem schnelleren und effizienteren Designprozess, größerem Erfolg beim „First Silicon“ und niedrigeren Herstellungskosten durch eine bessere Ausnutzung des 300-mm-Wafersubstrats und eine höhere Ausbeute.

Das Fraunhofer IZM hat diesen Trend schon früh aufgegriffen, indem es den Ansatz des „disaggregierten Systems" von oben nach unten verfolgte und dabei von seinem umfassenden Know-how im Bereich des Advanced Packaging profitierte.

Das Institut erkannte die Notwendigkeit eines von der Industrie akzeptierten Prozessstandards und war die erste Einrichtung in Europa, die auf spezifische F&E-Prozesse verzichtete und ein Hybrid-Bonding-Verfahren in Verbindung mit Through Silicon Vias bei sich einführte, welches heute in der gesamten Branche als Standard gilt.

Das Vorantreiben der Micro-Bumping-Technologie für Flip-Chip-Verbindungen mit extremen Kontaktdichten, die wir heute im Chip-Stacking sehen, ist ein langjähriges Anliegen des Fraunhofer IZM und seit nunmehr 30 Jahren Bestandteil der Innovationsstrategie des Instituts. Das Chiplet-Paradigma, das bereits die Front-End-Architektur in separate IP-zentrierte Hardware-Blöcke aufteilt, nutzt folgerichtig diese Packaging-Toolbox für die Integration zu einem hochfunktionalen System.

Ergänzt wird dieser bislang rein auf die digitale Domäne bezogene Architekturansatz durch den Trend zur heterogenen Integration.

Die technologischen Möglichkeiten in Verbindung mit dem Ansatz der Chiplet-Architektur erlauben inzwischen die Integration mehrerer Technologien wie Logik, Speicher, Analogtechnik und Sensoren auf einem einzigen chipgroßen (Sub-)System, was zu einem hochfunktionalen Modul mit verbesserter Leistung und Energieeffizienz führt.

Auch die weiter oben in der Wertschöpfungskette angesiedelten Elemente der Verpackungshierarchie haben ihrerseits Innovationsansätze zu bieten, die das sogenannte High-End-Performance-Packaging (HEPP) auszeichnen.

Diese HEPP-gestützte Integration wird vorangetrieben durch das Aufkommen des substratlosen Fan-Out-Packagings, das ultrahohe Leiterbahn- und Kontaktdichten auf großen Fertigungspaneelen, die Integration aktiver Interposer und geometrieinhärenter Merkmale (z. B. Richtantennen, integrierte Kühlung) ermöglicht und damit einen einfachen Pfad zur Heterointegration bietet.

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM